-

|

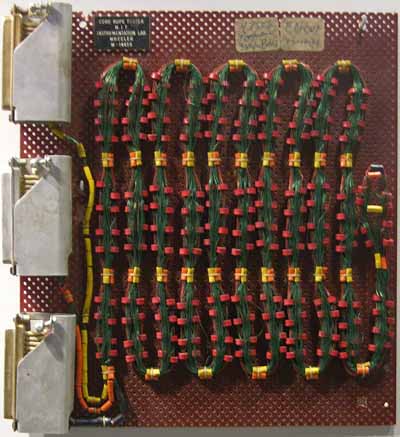

Mais il existe également une mémoire ROM à tores appellée rope core mémory (mémoire à cordes de ferrite). Ler mot "corde" est la traduction litérale du mot rope. Ce type de mémoire est moins connu, pourtant il était utilisé pour stocker le firmware de quelques ordinateurs des années 1950 et 1960. Il était également utilisé pour stocker le programme du module lunaire des missions Apollo. La mémoire à cordes a été choisie car elle est permanente, fiable et ne nécessite de la puissance que lors de la lecture. C'est aussi le type de mémoire la plus compacte de l'époque. La mémoire à cordes n'était pas souvent utilisée pour le stockage de firmware d'ordinateurs commerciaux, car elle était complexe à fabriquer et le contenu ne pouvait pas être modifié. Le fonctionnement de la mémoire morte est totalement différente de celle de la mémoire vive. Il n'est pas possible de modifier les données, et un bit incorrect nécessite de reconstruire la mémoire à partir de zéro. Les tores de ferrite ne sont pas utilisés pour le stockage d'un bit, mais ils sont utilisés comme une sorte de transformateur: une impulsion est produite dans le fil de lecture lors du changement de polarité. Ici aussi il faut un signal d'une amplitude minimale pour produire un changement de polarité.

Il y a une ligne set/reset qui va magnétiser dans un sens et puis dans l'autre sens les tores. Cette ligne passe par tous les tores. La mise à zéro se fait par un courant de gauche à droite du fil set/reset et les magnétise dans la position de repos. Chaque tore est une position d'adresse et les bits de données sont déterminés par les fils de lecture qui passent par le tore (produisent un 1) et par les fils de lecture qui ne passent pas par le tore en question (produisent un 0). Lors de la lecture, on met l'adresse voulue sur les lignes d'adressage (courant de gauche à droite), ce qui va bloquer le changement de polarité de tous les tores, sauf celui à l'adresse voulue. La ligne set/reset recoit maintenant une impulsion (courant de droite à gauche) qui va magnétiser en sens inverse le tore sélectionné par les lignes d'adressage. Ce changement de polarité est détecté par toutes les lignes de lecture (sense lines) qui passent par le tore et pas par les lignes qui ne passent pas par le tore. Après la lecture on envoie un courant de remise à zéro sur la ligne set/reset. Une seule ligne inhibit activée suffit pour bloquer le tore et empècher son changement de polarité (fonction NOT OR ou NOR). Plusieures lignes inhibit activées ne produisent pas un effet différent dans le tore. En pratique (voir image) les lignes d'adressage (inhibit lines) ont sélectionné le tore à l'adresse 2 (aucune ligne activée ne passe par le tore, qui est ainsi sélectionné). Il se produit un pic de tension sur les lignes de lecture 2 et 16, les autres lignes ne recevant pas de pic de tension. A l'adresse 1 on a une donnée 1, à l'adresse 3 on a une donnée 2 et à l'adresse 4 une donnée 1 + 2. Si on utilise une mémoire à cordes comme mémoire ROM, c'est parce qu'elle permet de stocker plus de bits dans un seul tore. Dans la mémoire RAM, chaque tore ne peut stocker qu'un bit d'information. Nous avons vu dans l'exemple que le tore produit un seul mot (15 bits + 1 bit de parité), mais il est possible de stocker plus d'un mot par tore: il y a 192 fils de lecture qui peuvent passer par le tore, permettant d'encoder 12 mots (192 lignes = 192 bits = 16 bits × 12 mots).

Le nombre de lignes d'adresses détermine le nombre de tores de mémoire qui peuvent être adressés. Il faut 2 lignes de sélection pour 4 tores, mais dans la mémoire à cordes il faut également la valeur inverse, il faut donc 4 lignes d'adresses. Pour 8 bits il faut 2 fois 3 lignes d'adresses, pour 16 bits il faut 2 fois 4 lignes, et ainsi de suite. Une unité de mémoire AGC ROM avait 512 tores, donc 6144 mots (512 cores × 12 mots) et nécessitait 18 fils d'adressage (2 × 9 adresses). Au maximum il y a 205 fils qui passent par un tore de la mémoire de l'ordinateur du module Apollo (192 fils de lecture, 18 fils d'adressage et un fil de set/reset). 6144 mots (de 16 bits) correspondent à 12k de mémoire "moderne". A gauche une mémoire à corde avec les nombreux fils qui passent (ou ne passent pas) par chaque tore. |

Publicités - Reklame