-

Comment fonctionne une mémoire à tores de ferrite (mémoire à tores magnétiques)

La mémoire à tores de ferrites est apparue dans les années 1950 et a continué a être utilisée jusque dans les années 1970. Ce type de mémoire avait de nombreux avantages:

Les tores de ferrite étant commandées en courant (et non en tension), les mémoires à tores de ferrite ont surtout été utilisées sur les systèmes à transistors et non à lampes.

Sélection d'un tore (ligne X et Y)Evidemment, c'est pas l'idéal s'il faut un fil par tore: cela rendrait le système vraiment complexe. On va utiliser le phénomène de l'hystérésis pour sélectionner un tore spécifique. Les tores sont montés dans un croisillon et chaque tore est traversé par deux fils, chaque fil étant parcouru par la moitié du courant nécessaire pour magnétiser un tore.

Cette procedure nous permet donc de sélectionner un tore (un bit d'information) avec une adresse. L'hysteresis de la ferrite agit comme une fonction AND logique: ce n'est que si les deux demi-courants sont présents que la ferrite est influencée. Si nous avons par exemple 2× 8 lignes de sélection nous avons une mémoire de 64 bits. Le bus d'adresse du processeur doit alors avoir une longueur de 6 bits (000 000 à 111 111, valeurs décimales de 0 à 63). Un circuit transforme les 6 bits du bus d'adresse en 2×8 lignes de commande. Un petit truc permet de réduire de moitié le nombre de lignes dans un plan (X ou Y), c'est la coïncidence. Dans les examples nous utilisons le plan Y. Si le courant dans les deux fils sont dans le même sens, ils produisent un champ magnétique qui s'additionne dans le tore. Si le courant est dans un sens contraire, les champs magnétiques s'annulent. Ce truc n'est pas utilisé dans toutes les mémoires.

Avec seulement un fil, on peut commander deux tores dans le plan Y selon la polarité du fil X et Y:

Lecture de l'information magnétique stockée dans un tore (ligne sense)Voila, nous avons une mémoire qu'on peut écrire, mais qu'on ne peut pas lire! Heureusement, quand le tore change de polarité, il produit un petit champ magnétique (il fonctionne alors en fait comme un petit transfo). Pour lire le changement de polarité d'un tore, nous avons un fil qui passe par tous les tores, le fil sense.Quand aucun tore ne change de polarité magnétique, la tension induite est minimale, s'il y a un changement de polarité, la tension est plus importante. La lecture étant destructive, il faut directement réécrire le bit après sa lecture. Comme les processeurs travaillent souvent selon le cycle READ-MODIFY-WRITE (lire une valeur de la mémoire, la modifier et la replacer en mémoire), le circuit de controle de la mémoire attend un cycle du processeur: cela permet d'éviter une opération d'écriture inutile. Dans l'exemple ci-dessous utilise une impulsion de 2µs. Dans les systèmes récents l'impulsion est inférieure à 1µs, temps nécessaire pour vaincre la self-induction du tore de ferrite.

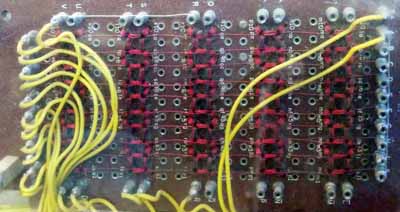

Et finalement, nous avons notre construction terminée, avec les fils de sélection et le fil de lecture:

Ecriture d'un tore (ligne inhibit) Bleu et vert: fils de sélection x, y

Bleu et vert: fils de sélection x, yViolet: Sense Orange: Inhibit Dans les types plus anciens, il y a un second fil qui circule avec le fil de sélection X (ou Y): c'est le fil inhibit. Ce fil passe par tous les tores comme le fil sense, mais pour éviter les interférences il passe horizontalement (ou verticalement). Dans les systèmes plus récents, on utilise le même fil "sense" comme fil "inhibit". Le fil "inhibit" sert à l'écriture, pour bloquer l'écriture d'un bit. Le fil inhibit contient en fait la donnée à écrire. On aurait pu ne rien écrire pour écrire un "0", mais c'est plus simple du point de vue électronique si on utilise un adressage indépendant et un fil de données.

L'exemple à droite nous montre un système qui utilise des mots de 7 bits (le bus de données a une largeur de 7 bits). Les 7 cadres sont entassés les uns sur les autres et les fils de sélection servent pour tous les tores des cadres. La raison de l'utilisation d'un inhibit (fil séparé ou combiné avec sense) est purement technique. Pour permettre de simplifier les circuits, les lignes de sélection servaient uniquement à la sélection d'un tore: la non-écriture étant réalisé par un courant de demi-intensité dans le fil inhibit (courant en sens contraire). Si le courant est présent, il empèche l'écriture: +0.5 +0.5 -0.5 = +.5 qui est trop faible pour influencer le tore.

Chaque cadre a son fil sense/inhibit propre, dont le signal après conditionnement est placé sur le bus de données. L'adressage est valable pour tous les cadres. Quand un mot est lu à la position (X, Y), tous les bits sont accédés simultanément car les fils d'adressage sont branchés en série. Encore quelques petites données techniques (types récents):

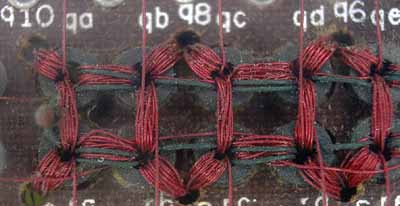

Ce sont les tores qui reçoivent un demi-courant qui produisent un faible champ parasite, et donc un faible signal induit dans le fil sense. C'est pour réduire cet effet que les tores sont montés en alternance (inclinés à gauche puis à droite): l'effet d'un tore incliné à gauche est réduit par l'effet contraire du tore suivant incliné à droite.

Tores de mémoire et tores de sélectionUne mémoire de 4096 bit par cadre a besoin de deux fois 64 lignes de sélection (64×64 = 4096), ce qui fait quand même beaucoup, alors que le but de la mémoire à tores de ferrite est justement de réduire le nombre de circuits électroniques.On aurait autrement pu utiliser deux transistors (mémoire flip flop) pour stocker un bit. C'est ce qui se fait actuellement, car les puces de mémoire peuvent contenir des millions de transistors. Mais à cette époque, on tentait d'en limiter le nombre. Un transistor avait un diamètre de 8.9mm (format TO-5 le plus courant), alors qu'un tore faisait moins d'un mm de diamètre.

Notre mémoire de 4096 bits peut maintenant être commandée par deux fois 8 lignes de sélection (8×8 = 64). Le bus d'adresses doit être de 12 bits pour permettre d'accéder à tous les bits de la mémoire. Ici aussi, plusieurs cadres sont mis en parallèle pour former des mots de 8, 12, 16,... bits (selon l'architecture du processeur). Les tores qui sont utilisés comme transfo sont plus grands, puisque le courant nécessaire au secondaire est plus important (il doit permettre de commuter les tores de mémoire). On utilise également plusieurs spires aux deux primaires et au secondaire, ce qui permet d'avoir un champ magnétique déterminé avec un courant moindre. Nous avons donc un cadre avec ses 4096 bits de données (4096 tores de mémoire) et 2×64 tores de sélection. Le nombre de tores de sélection est fixe, quel que soit la longueur d'un mot (nombre de cadres entassés). Il ne s'agit pas d'un transfo haute fréquence classique (comme ceux utilisés dans les alimentations à découpage) qui utilise de la ferrite "douce" (aisément magnétisable), mais de transfos à ferrite "dure" qui nécessite un courant de magnétisation important. C'est nécessaire pour que le demi-courant de sélection ne soit pas transmis au secondaire. Le transfo ne peut transmettre une impulsion que quand il reçoit un courant nominal de sélection. Les tores de sélection ont encore un fil supplémentaire appelé bias qui produit un champ constant permettant une commutation correcte. Les tores qui agissent comme transfo déforment l'impulsion de sélection, mais la forme est encore suffisamment correcte pour agir sur les tores de la mémoire. Le courant de sélection est "déformé" à priori pour produire une impulsion de forme correcte. Un double étage est par contre impossible à réaliser, l'impulsion de sélection finale n'est pas conforme. La photo à droite reprend quelques tores de sélection de l'IBM 1400. Chaque tore de sélection a deux primaires et un secondaire. Le secondaire est le bobinage en oblique (celui qui ne relie pas deux tores).

La suite: Rope core memory: il existe également une mémoire ROM (mémoire morte) basée sur les tores de ferrite, mais son fonctionnement est totalement différent. |

Publicités - Reklame

Nous avons déjà appris que quand un conducteur électrique est parcouru par un courant, il développe un champ magnétique qui peut magnétiser le tore si le courant est suffisamment important.

Nous avons déjà appris que quand un conducteur électrique est parcouru par un courant, il développe un champ magnétique qui peut magnétiser le tore si le courant est suffisamment important.

Comme exemple nous avons une mémoire avec 16 tores et 2 fois 4 fils de sélection. Nous envoyons le courant de sélection dans un fil X et un fil Y.

Comme exemple nous avons une mémoire avec 16 tores et 2 fois 4 fils de sélection. Nous envoyons le courant de sélection dans un fil X et un fil Y.

Dans la mémoire, les bits sont assemblés sous forme de mots. Si les ordinateurs actuels sont passés de 8 à 16 puis 32 et 64 bits, les premiers ordinateurs pouvaient avoir un bus de données de 22 ou 24 bits, dépendant de l'architecture du système.

Dans la mémoire, les bits sont assemblés sous forme de mots. Si les ordinateurs actuels sont passés de 8 à 16 puis 32 et 64 bits, les premiers ordinateurs pouvaient avoir un bus de données de 22 ou 24 bits, dépendant de l'architecture du système.